# **TÉCNICAS Y ESTRUCTURAS DIGITALES**

Tema: Memorias - Posicionamiento y Ampliación

Ingeniería Informática – Licenciatura en Sistemas

LU:

Apellido y Nombre:

Carrera: Fecha:

**12**

# Problems a Resource

### 1. Teoría:

- a) Conceptualice mapa de direcciones.

- b) ¿En qué lugar del mapa de direcciones se suelen ubicar las memorias RAM y ROM? Justifique.

- c) ¿Qué es la línea de selección de chip (CS)? ¿Qué ocurriría con la memoria si no existiera el terminal CS?

- d) ¿Qué función cumple la línea OE?

- e) ¿Qué es la memoria fantasma? ¿En qué casos puede producirse?

- f) ¿Por qué se dice que la producción de memoria fantasma es nociva?

- g) ¿Qué es la asociación de registros de memoria? Al asociar memorias ¿qué condiciones generales debe considerar?

- h) Ejemplifique y grafique una ampliación de la cantidad de registros de memoria.

- i) Ejemplifique y grafique una ampliación de longitud de registros de memoria.

- 2. Complete la siguiente tabla teniendo en cuenta la características arquitectónicas indicadas para cada sistema:

| Sistema               | Bus de<br>Direcciones<br>(m bits) | Bus de Datos<br>(n bits) | Tamaño del<br>Registro de<br>Memoria | Tamaño del<br>Mapa de<br>Direcciones | Total de bits<br>del mapa | Dirección Inicial y Final<br>del Mapa de Direcciones |

|-----------------------|-----------------------------------|--------------------------|--------------------------------------|--------------------------------------|---------------------------|------------------------------------------------------|

| S <sub>0</sub>        |                                   | 8                        |                                      |                                      |                           | \$000 - \$7FF                                        |

| <b>S</b> <sub>1</sub> | 25                                |                          | 16                                   |                                      |                           |                                                      |

| S <sub>2</sub>        |                                   |                          |                                      | 8 KB                                 | 65536                     |                                                      |

| S <sub>3</sub>        | 19                                | 8                        |                                      |                                      |                           |                                                      |

| S <sub>4</sub>        |                                   | 32                       |                                      |                                      |                           | \$000000 - \$7FFFFF                                  |

| S <sub>5</sub>        | 22                                |                          |                                      |                                      | 33554432                  |                                                      |

| S <sub>6</sub>        |                                   |                          | 16                                   |                                      |                           | \$00000 - \$3FFFF                                    |

3. Dado un mapa de direcciones de 32.768 palabras (de 8 bits) y los bloques de memorias RAM y ROM indicados a continuación, complete la tabla identificando los bits del AB usados para direccionamiento interno y selección de chip de cada bloque de memoria así como las direcciones iniciales/finales correspondientes.

| Tipo de<br>Bloque | Dirección<br>Inicial | Dirección<br>Final | Tamaño de<br>Bloque (bytes) | Selección de<br>Chip (bits)      | Direccionamiento<br>Interno (bits) |

|-------------------|----------------------|--------------------|-----------------------------|----------------------------------|------------------------------------|

| RAM1              | \$1000               |                    | 4096                        |                                  |                                    |

| RAM2              |                      | \$43FF             |                             | A <sub>14</sub> -A <sub>10</sub> |                                    |

| RAM3              | \$4400               |                    | 1024                        |                                  |                                    |

| ROM1              |                      | \$5FFF             |                             |                                  | A <sub>10</sub> -A <sub>0</sub>    |

| ROM2              |                      | \$7FFF             | 8192                        |                                  |                                    |

|                   |                      |                    |                             |                                  |                                    |

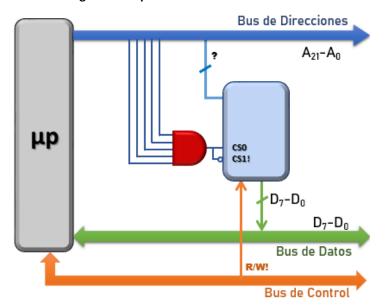

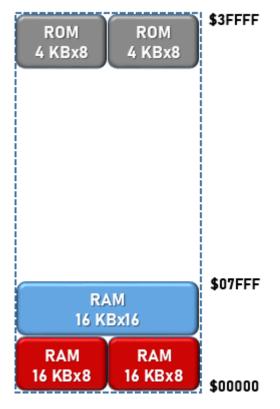

### 4. Dado el siguiente esquema

- a) ¿Cuál es el tamaño del mapa de direcciones?

- b) ¿De qué tipo y tamaño es la memoria del esquema?

- c) ¿Cuál es el rango de direcciones ocupado por el bloque de memoria?

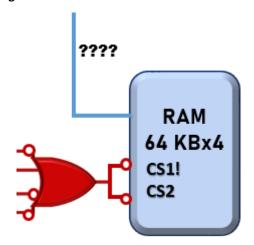

- d) ¿Cuántos bloques de memoria 64KBx4 serán necesarios para reemplazar el que aparece en la figura? Modifique el esquema mostrando este cambio.

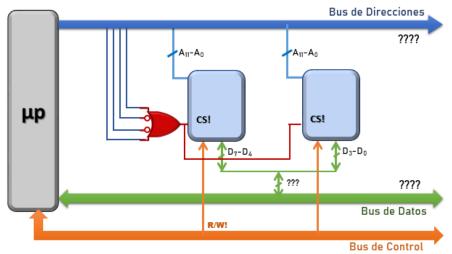

#### 5. Dado el siguiente esquema

- a) ¿Cuál es el tamaño del mapa de direcciones y el ancho del bus de datos?

- b) ¿De qué tipo y tamaño son los bloques del esquema?

- c) ¿Cuál es el rango de direcciones ocupado por los bloques de memoria?

- d) ¿Cómo se modifica el esquema si en lugar de usar bloques de memoria Nx4, sólo dispone de bloques Nx2? (N indica la cantidad de registros o palabras de la memoria)

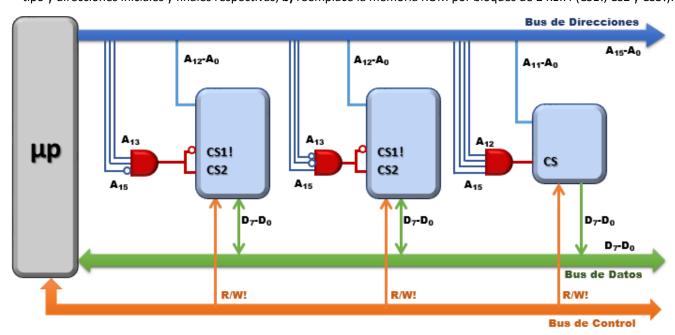

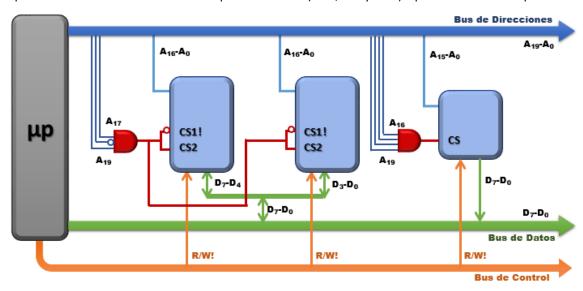

- **6. Dado el siguiente esquema de conexión: a)** dibuje el mapa de direcciones correspondiente e indique, por cada bloque, tipo y direcciones iniciales y finales respectivas; **b)** reemplace la memoria ROM por bloques de 2 KBx4 (CS1!, CS2 y CS3!).

7. Dado un sistema anfitrión en el que se instaló el siguiente bloque de memoria RAM, determine: ¿cuál es el ancho del bus de direcciones y del bus de datos? ¿cuál es el tamaño del mapa de direcciones? ¿cuáles son las direcciones iniciales y finales de la RAM? ¿Cuál es el rango de direcciones libres?

- 8. Dado un sistema que dispone de un bus de direcciones (AB) de 16 líneas y un bus de datos (DB) de 8 bits, deben instalarse 1 KB de memoria RAM (a partir de la dirección \$2400) y 4 KB de memoria ROM (al final del mapa). Considere que se dispone de suficientes bloques RAM de 512 Bytes x8 (CS!) y bloques ROM de 2KBx8 (CS1!, CS2). Sabiendo esto:

- a) ¿Cuál es el tamaño del mapa de direccionamiento?

- b) Dibuje el mapa de direcciones correspondiente indicando direcciones iniciales y finales de los bloques de memoria instalados.

- c) Realice el esquema de conexión correspondiente.

- d) ¿Qué líneas del AB se utilizan para la activación del CS y cuáles para el direccionamiento interno de la RAM?

- e) ¿Qué líneas del AB se utilizan para la activación del CS y cuáles para el direccionamiento interno de la ROM?

- 9. Dado el siguiente esquema:

- a) ¿Cuál es el tamaño del mapa de direcciones?

- b) ¿Cuál es la dirección inicial/final de cada bloque de memoria?

- c) Realice el esquema de conexión correspondiente.

- 10. Dado un sistema anfitrión de 20 líneas de direcciones y 16 líneas de datos, instale una unidad de memoria RAM de 16 KBx8 con dos líneas de selección de chip CS1! y CS2! a partir de la dirección \$20000.

- a) Suponiendo que la línea A<sub>19</sub> del sistema sufrió una corrosión y quedó desconectada ¿Qué ocurre en el sistema? ¿Qué inconvenientes se presentan?

- b) ¿Y qué ocurriría si se desconectan las líneas, A<sub>19</sub> y A<sub>18</sub>?

- c) Si en cambio, la línea corroída hubiera sido la menos significativa (A<sub>0</sub>) ¿qué ocurriría?

Cuando las líneas del bus de direcciones no se utilizan en su totalidad para activar la selección del chip de memoria, aquellas líneas que quedan sin conexión pueden asumir cualquier valor lógico produciéndose igualmente la selección de la unidad de memoria. Estos significa que el mismo bloque de memoria se representará 2<sup>n</sup> veces (siendo n la cantidad de líneas no conectadas) en el mapa de memoria, produciendo el efecto denominado memoria fantasma.

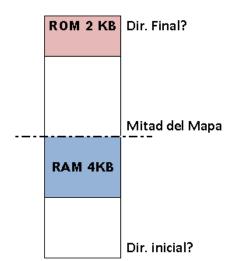

11. Dado un sistema que puede direccionar 16384 registros, y leer/escribir 16 bits al acceder memoria, instale en él una memoria RAM de 4 KB y una memoria ROM de 2 KB según se indica en el siguiente mapa de direcciones

- a) Utilice bloques de 4 KBx8 (CS) para configurar la RAM y bloques 2KBx16 (CS1,CS2!) para configurar la ROM

- b) Determine las direcciones iniciales y finales del mapa y de cada bloque

- c) Realice el esquema de conexión correspondiente

- 12. Dado un sistema capaz de direccionar 262.144 registros y leer/escribir 8 bits al acceder memoria; instale una memoria RAM de 32 KB a partir de la dirección \$28000.

- a) Utilice bloques de 16 KBx4 (CS1, CS2!, CS3!) para configurar la RAM.

- b) Dibuje el mapa de direccionamiento, determine las direcciones iniciales y finales del mapa y de cada bloque.

- c) Realice el esquema de conexión correspondiente.

- 13. Dado un sistemas anfitrión con un bus de datos de 16 bits en el que se instalan 3 bloques de memoria (cuyas direcciones iniciales y finales se indican en la siguiente tabla) determine:

| Bloque   | Inicio | Fin    | CS       | Tipo Memoria | Tamaño |

|----------|--------|--------|----------|--------------|--------|

| Bloque 1 | \$6000 | \$7FFF | CS!      |              |        |

| Bloque 2 | \$6000 | \$7FFF | CS!      |              |        |

| Bloque 3 | \$FE00 | \$FFFF | CS1 CS2! |              |        |

- a) Tipo y tamaño de cada bloque.

- b) Las direcciones iniciales y finales de cada bloque en el mapa de direcciones. Indique la primera y última dirección del mapa.

- c) Esquema de conexión correspondiente.

- 14. En un sistema que posee un bus de datos de 8 líneas, las direcciones de inicio y fin de 3 bloques de memoria ubicados en el mapa de direcciones, son las siguientes:

| Bloque   | Inicio | Fin    | CS        | Tipo Memoria | Dimensión |

|----------|--------|--------|-----------|--------------|-----------|

| Bloque 1 | \$5000 | \$5FFF | CS1!, CS2 |              |           |

| Bloque 2 | \$FE00 | \$FFFF | CS!       |              |           |

| Bloque 3 | \$FE00 | \$FFFF | CS!       |              |           |

- a) Complete el tipo de memoria y la dimensión de cada bloque.

- b) Dibuje el mapa de direcciones, indicando los 3 bloques de memoria y sus respectivas direcciones.

- c) Realice el esquema de conexión correspondiente.

- **15.** Dado el siguiente esquema de conexión: a) dibuje el mapa de direccionamiento (indicando tipo de bloques y direcciones iniciales y finales de los bloques y mapa de direcciones) y b) agregue en el mapa de direcciones y en el esquema de conexión un bloque de memoria RAM de 8 KB con bloques de 4 KB x 8 (CS1!, CS2 y CS3!) a partir de la mitad superior del mapa.

: : :

Página 5