Contenido

## TECNICAS Y ESTRUCTURAS DIGITALES

PROFESORES MG. SERGIO L. MARTINEZ - ING. VICTOR D. SANCHEZ R.

Unidad 3.2 - CIRCUITOS LÓGICOS COMBINACIONALES

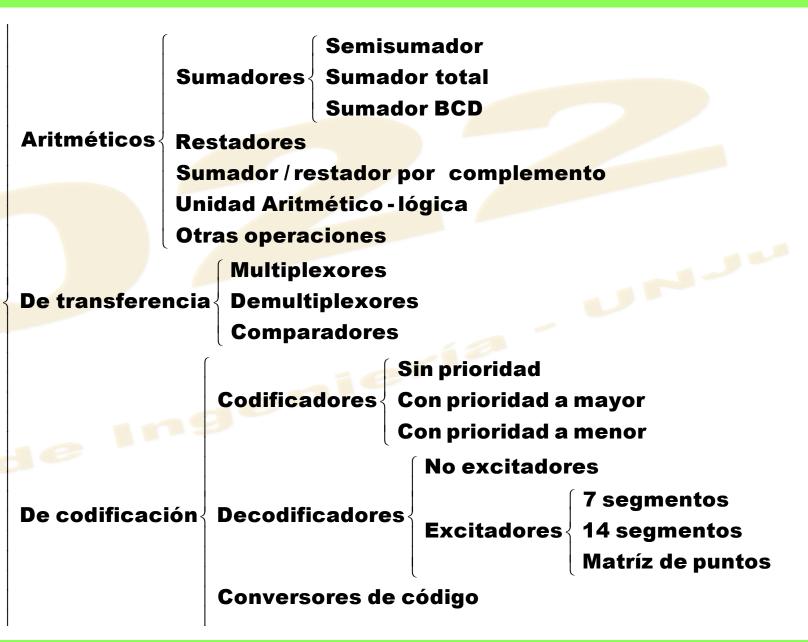

## CIRCUITOS COMBINACIONALES ESTÁNDARES

- Circuitos Aritméticos Sumadores Restadores ALU

- De transferencia de datos Multiplexores Demultiplexores Comparadores

- De codificación

Codificadores

Decodificadores

Conversores

- Ejemplos

- > Floyd T. (2006). FUNDAMENTOS DE SISTEMAS DIGITALES. Capítulo 3: Puertas lógicas; capítulo 5: Análisis de lógica combinacional.

- > Ramos J. (2012). SISTEMAS DIGITALES. Capítulo 3: Lógica combinacional.

- > Mano M. (2003). DISEÑO DIGITAL. Capítulo 4: Lógica combinacional.

- > Brown S. (2006). FUNDAMENTOS DE LÓGICA DIGITAL CON DISEÑO VHDL. Capítulo 2: Introducción a los circuitos lógicos.

- > Tocci R. (2007). SISTEMAS DIGITALES PRINCIPIOS Y APLICACIONES. Capítulo 4: Circuitos lógicos combinacionales.

#### CIRCUITOS LÓGICOS COMBINACIONALES

#### **Definición**

Son aquellas configuraciones de *n* entradas y *m* salidas, tal que su salida o salidas dependen exclusivamente del estado *actual* de sus variables de entrada, independientemente del factor *tiempo*.

Todo circuito lógico combinacional representa a una determinada función lógica que no contiene componentes de realimentación.

El flujo de señales es unidireccional, de la entrada hacia la salida.

## **COMBINACIONALES ESTÁNDARES**

## Concepto

Son estructuras combinacionales de uso frecuente y muy difundido, por lo que existen disponibles comer-cialmente como circuitos integrados listos para ser utilizados.

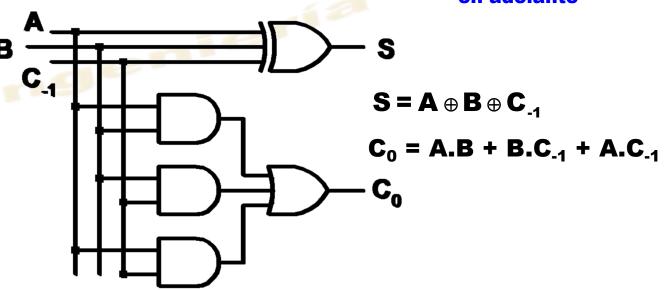

## **SUMADORES**

#### **Sumadores**

| A | В | S | С |        |

|---|---|---|---|--------|

| 0 | 0 | 0 | 0 | A      |

| 0 | 1 | 1 | 0 | + B    |

| 1 | 0 | 1 | 0 | (c ← s |

| 1 | 1 | 0 | 1 |        |

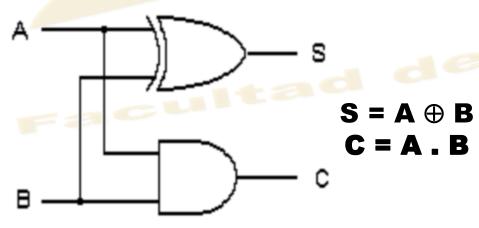

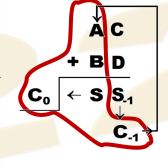

#### **Semisumador**

suma la primera columna

| A | В | <b>C</b> -1 | s | Co |

|---|---|-------------|---|----|

| 0 | 0 | 0           | 0 | 0  |

| 0 | 0 | 1           | 1 | 0  |

| 0 | 1 | 0           | 1 | 0  |

| 0 | 1 | 1           | 0 | 1  |

| 1 | 0 | 0           | 1 | 0  |

| 1 | 0 | 1           | 0 | 1  |

| 1 | 1 | 0           | 0 | 1  |

| 1 | 1 | 1           | 1 | 1  |

Floyd, pg. 328 Mano, pg. 119 Dormido, pg. 182

Sumador total suma la 2º columna en adelante

$C_0 = 0$

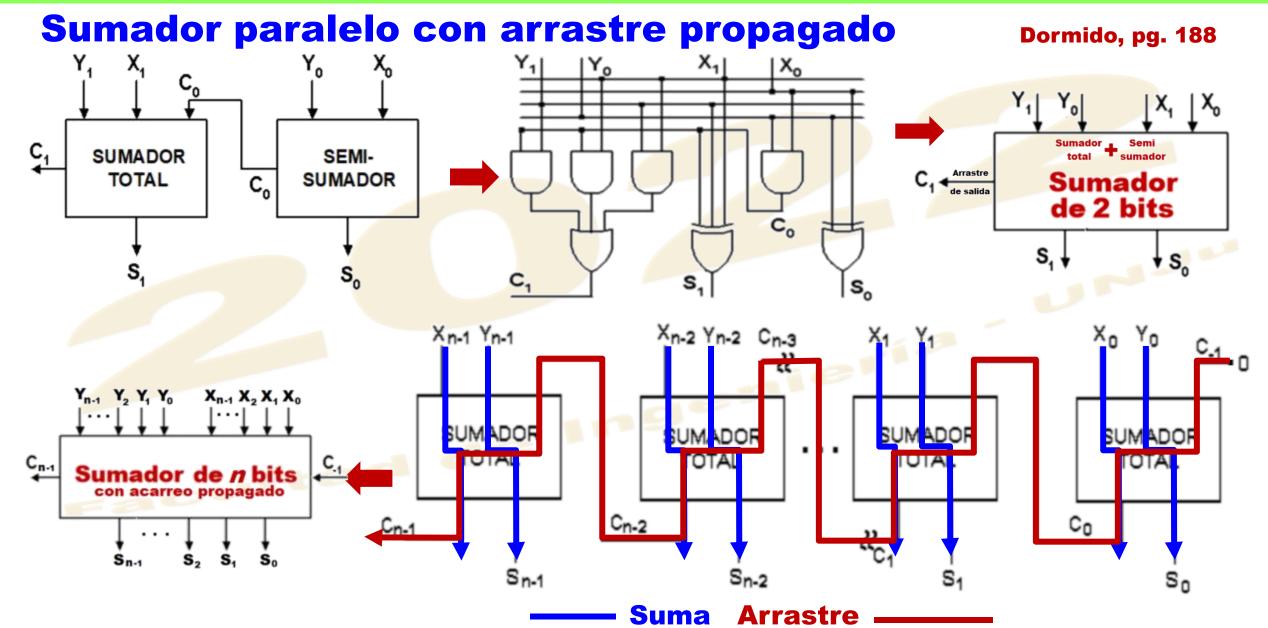

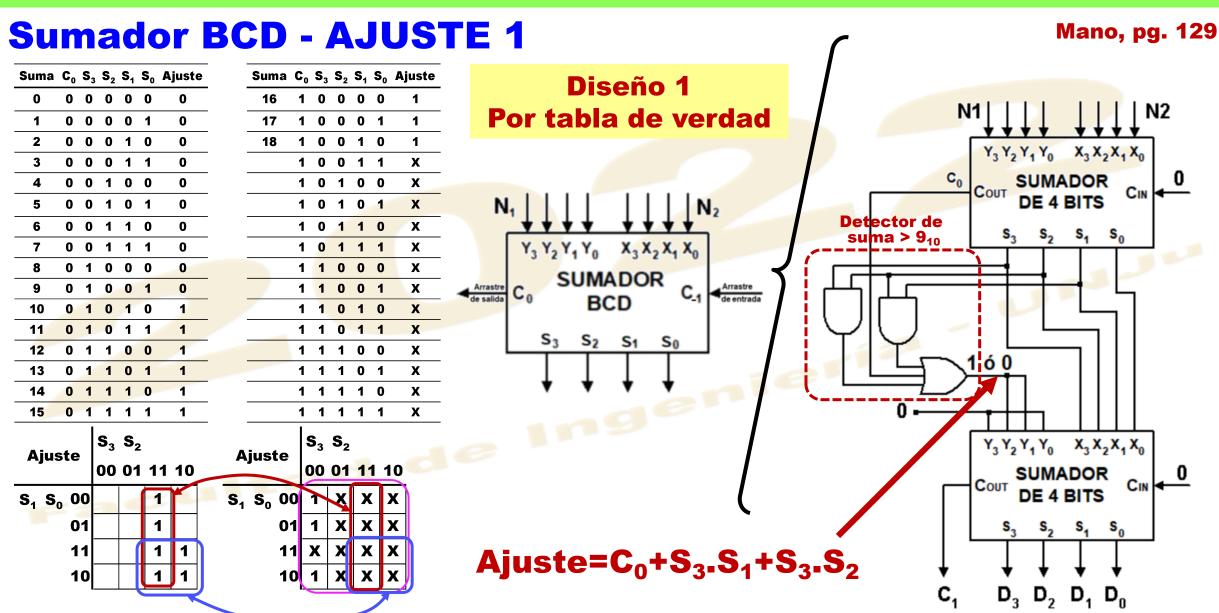

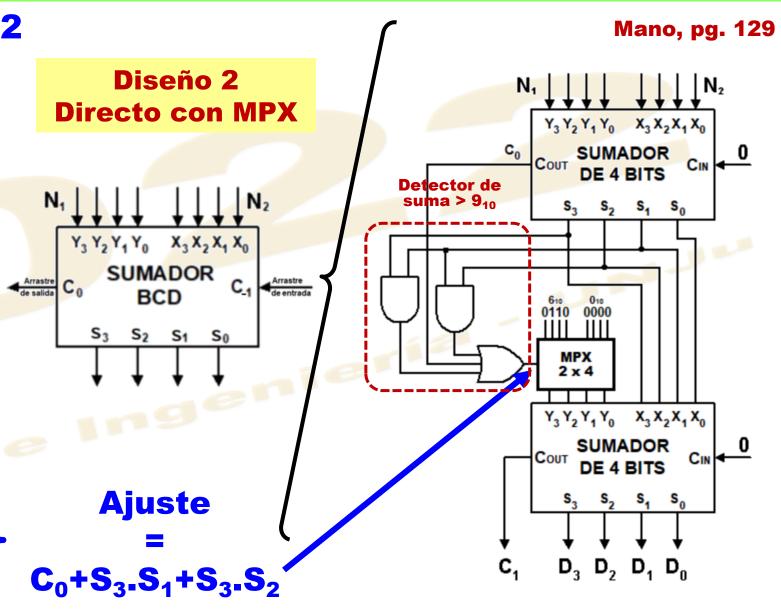

#### **Sumador BCD - AJUSTE 2**

| Suma | C. | S. | S. | S | S | Ajuste |

|------|----|----|----|---|---|--------|

| 0    | 0  | 0  | 0  | 0 | 0 | 0      |

| 1    | 0  | 0  | 0  | 0 | 1 | 0      |

| 2    | 0  | 0  | 0  | 1 | 0 | 0      |

| 3    | 0  | 0  | 0  | 1 | 1 | 0      |

| 4    | 0  | 0  | 1  | 0 | 0 | 0      |

| 5    | 0  | 0  | 1  | 0 | 1 | 0      |

| 6    | 0  | 0  | 1  | 1 | 0 | 0      |

| 7    | 0  | 0  | 1  | 1 | 1 | 0      |

| 8    | 0  | 1  | 0  | 0 | 0 | 0      |

| 9    | 0  | 1  | 0  | 0 | 1 | 0      |

| 10   | 0  | 1  | 0  | 1 | 0 | 1      |

| 11   | 0  | 1  | 0  | 1 | 1 | 1      |

| 12   | 0  | 1  | 1  | 0 | 0 | 1      |

| 13   | 0  | 1  | 1  | 0 | 1 | 1      |

| 14   | 0  | 1  | 1  | 1 | 0 | 1      |

| 15   | 0  | 1  | 1  | 1 | 1 | 1      |

| Suma | Co | $S_3$ | S <sub>2</sub> | S <sub>1</sub> | S <sub>0</sub> | Ajuste |

|------|----|-------|----------------|----------------|----------------|--------|

| 16   | 1  | 0     | 0              | 0              | 0              | 1      |

| 17   | 1  | 0     | 0              | 0              | 1              | 1      |

| 18   | 1  | 0     | 0              | 1              | 0              | 1      |

|      | 1  | 0     | 0              | 1              | 1              | X      |

|      | 1  | 0     | 1              | 0              | 0              | X      |

|      | 1  | 0     | 1              | 0              | 1              | X      |

|      | 1  | 0     | 1              | 1              | 0              | Х      |

|      | 1  | 0     | 1              | 1              | 1              | X      |

|      | 1  | 1     | 0              | 0              | 0              | X      |

|      | 1  | 1     | 0              | 0              | 1              | Х      |

|      | 1  | 1     | 0              | 1              | 0              | X      |

|      | 1  | 1     | 0              | 1              | 1              | X      |

|      | 1  | 1     | 1              | 0              | 0              | X      |

|      | 1  | 1     | 1              | 0              | 1              | X      |

|      | 1  | 1     | 1              | 1              | 0              | X      |

|      | 1  | 1     | 1              | 1              | 1              | X      |

Detector marca 1 cuando hay arrastre (línea 16, 17 y 18)  $\rightarrow$  1° **término**Detector marca 1 para  $S_3$  y  $S_1$  = 1 (líneas 10 y 11)  $\rightarrow$  2° **término**Detector marca 1 para  $S_3$  y  $S_2$  = 1 (líneas 12 a 15)  $\rightarrow$  3° **término**

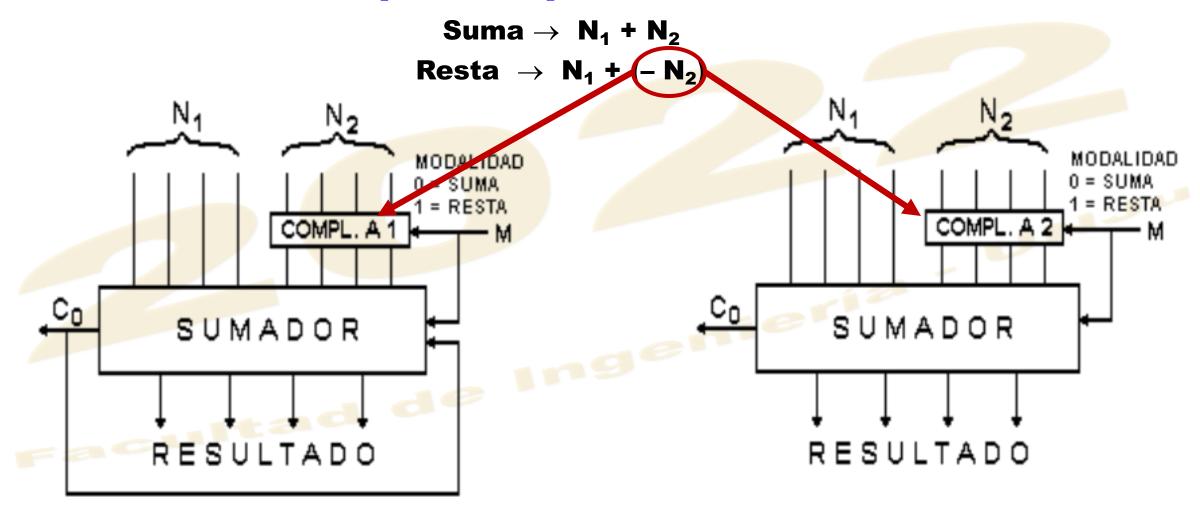

#### Sumador/restador por complemento

Ver Dormido, cap 4

Sumador / restador por complemento a 1

Sumador / restador por complemento a 2

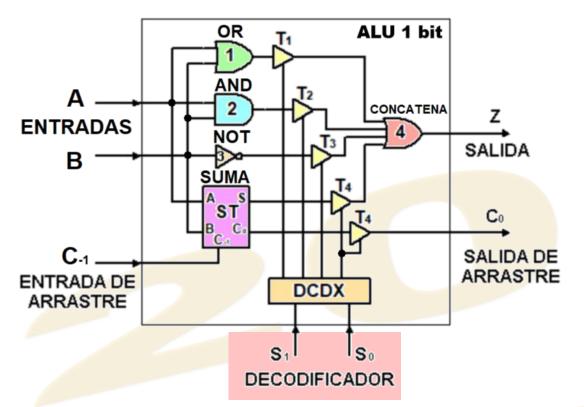

# A.L.U. UNIDAD ARITMÉTICO - LÓGICA

| CÓ        | digo       | tri- | state | que | se ac | ctiva |                      |

|-----------|------------|------|-------|-----|-------|-------|----------------------|

| <b>S1</b> | <b>S</b> 0 | T1   | T2    | Т3  | T4    | T4    | Operación            |

| 0         | 0          | 1    | 0     | 0   | 0     | 0     | A or B               |

| 0         | 1          | 0    | 1     | 0   | 0     | 0     | A and B              |

| 1         | 0          | 0    | 0     | 1   | 0     | 0     | B negado             |

| 1         | 1          | 0    | 0     | 0   | 1     | 1     | A + B con arrastre C |

## Unidad aritmético-lógica

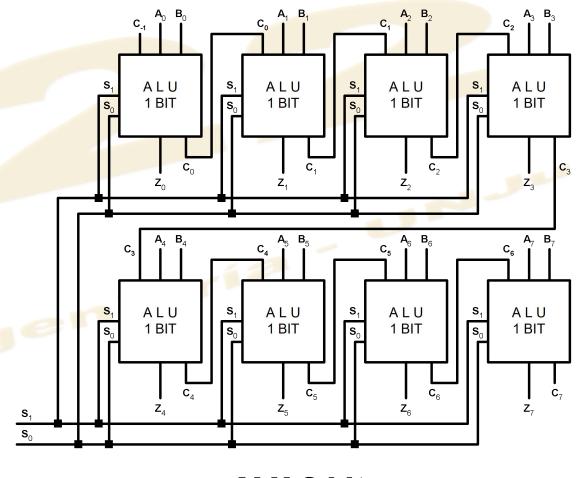

**ALU 8 bits**

Dormido, pg. 234

# MPX MULTIPLEXORES

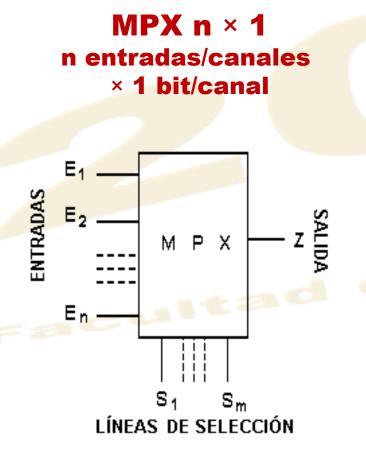

#### **Multiplexores (MPX)**

Floyd, pg. 367 - Mano, pg. 141 - Dormido, pg. 451

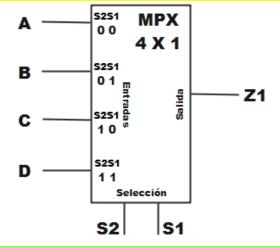

Un multiplexor puede definirse como un circuito lógico combinacional de varias entradas y una salida de tal forma que es posible "transferir" (reconstruir) una de las entradas a la salida mediante una codificación preestablecida.

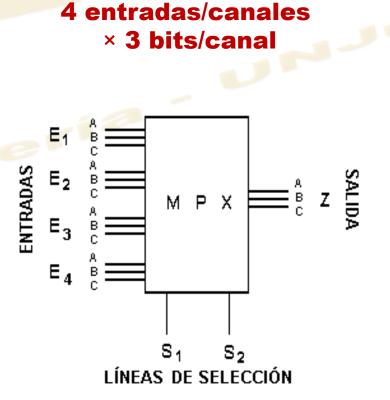

$MPX 4 \times 3$

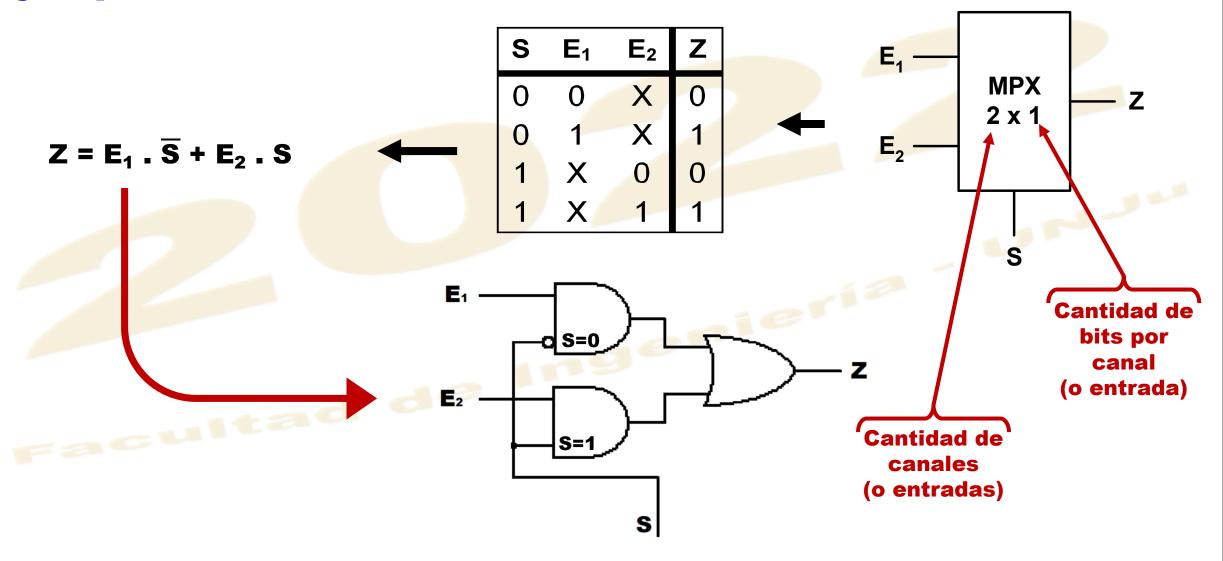

#### **Ejemplo:** Multiplexor de 2x1

#### **Multiplexor (MPX)**

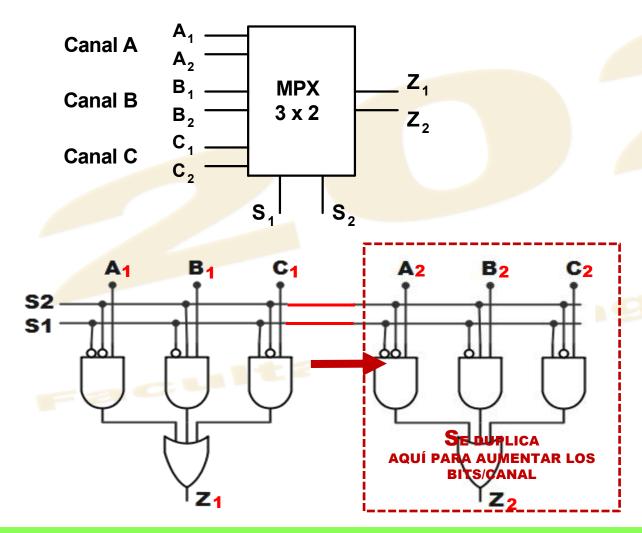

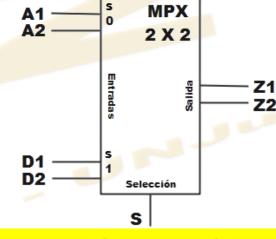

#### **Ejemplo:** Multiplexor de 3x2

Conviene siempre iniciar con un diseño MPX 2<sup>N</sup> x 1, luego reproducir la estructura hasta conseguir los bits/canal requeridos.

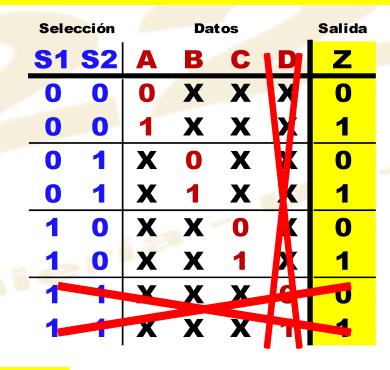

$$Z = \overline{S1.S2.A} + \overline{S1.S2.B} + S1.\overline{S2.C} + S1.S2.D$$

MPX 3X1

$$Z = \overline{S1.S2.A} + \overline{S1.S2.B} + S1.\overline{S2.C}$$

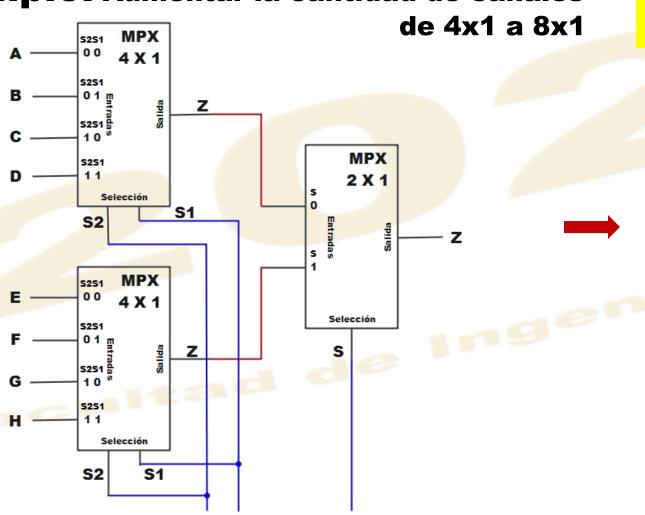

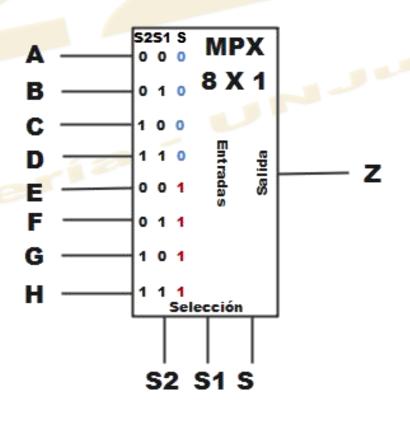

#### Multiplexores (MPX) - Asociación

Combinar o asociar multiplexores permite crear estructuras más complejas, utilizando bloques menores, con las que se puede multiplexar datos para (rel<mark>ativa</mark>mente) cualquier número de canales y de bits por canal.

Los criterios a seguir son simples:

> Al aumentar la cantidad de canales, generalmente debe aumentar la cantidad de J 84 J 24 líneas de selección, tal que

N° canales ≤ 2 (N° líneas selección)

significa: por lo menos una palabra de código de selección para cada canal.

- > Al aumentar la cantidad de bits por canal, no aumentan las líneas de selección. La nueva estructura debe conectar sus líneas de selección 'en bus' con las ya existentes.

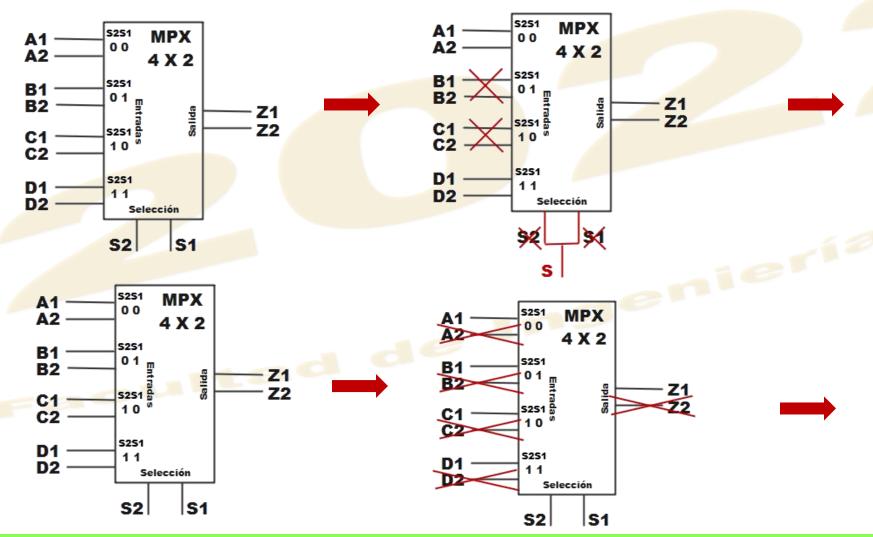

- > Para el diseño de estructuras de NxM (N=canales; M=bits), es buena práctica iniciar con un bloque de Nx1, multiplicar este formato y conectarlos, hasta alcanzar los M bits por canal.

- > Multiplexores de NxM se pueden reducir en cantidad de canales, omitiendo los que no se necesitan. Idem para los bits/canal.

#### Multiplexor (MPX) - Asociación

### Ejemplo: Reducción de multiplexores

#### Reducción de canales

#### Reducción de bits/canal

#### Multiplexor (MPX) - Asociación

**Ejemplo:** Aumentar la cantidad de canales

Para aumentar una línea de selección se agrega una nueva instancia de decisión (MPX 2x1) que seleccione las salidas del primer grupo.

S2 S1

### Multiplexores (MPX) - Asociación

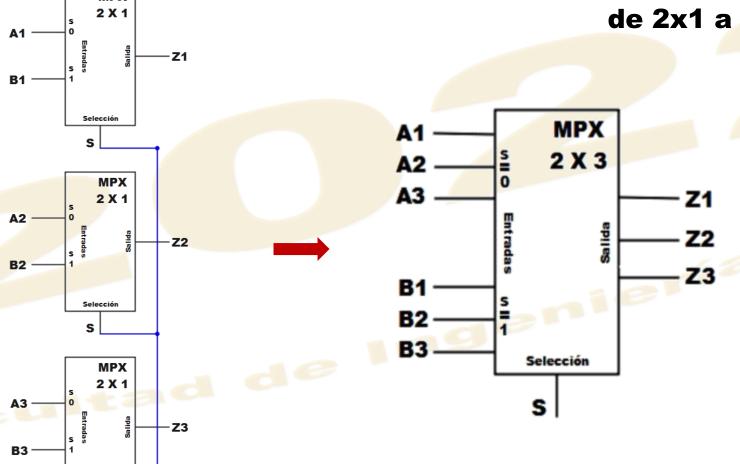

**Ejemplo:** Aumentar la cantidad de bits por canal, de 2x1 a 2x3.

Al aumentar la cantidad de bits por canal, no se modifica la cantidad de líneas de selección. La estrategia es conectar en bus, unidades con la misma cantidad de canales.

Selección

S

# DMPX DEMULTIPLEXORES

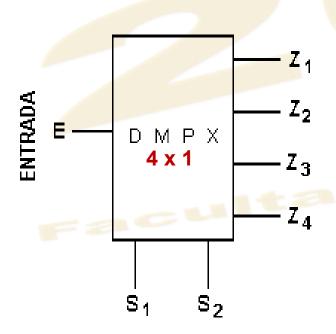

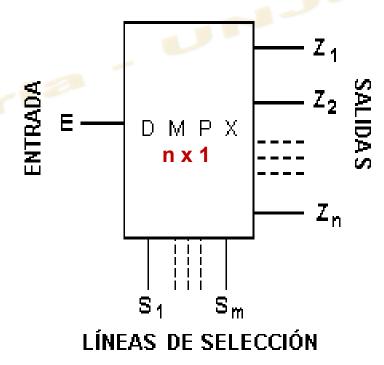

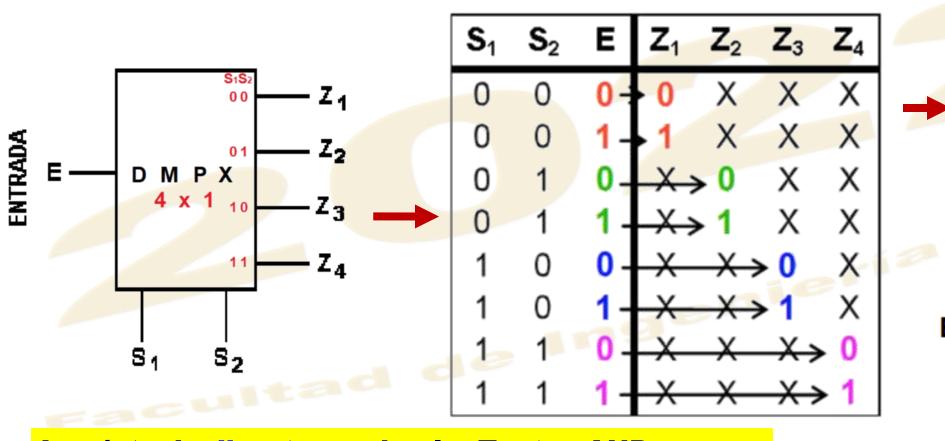

#### **Demultiplexores (DMPX)**

Floyd, pg. 377 - Dormido, pg. 454

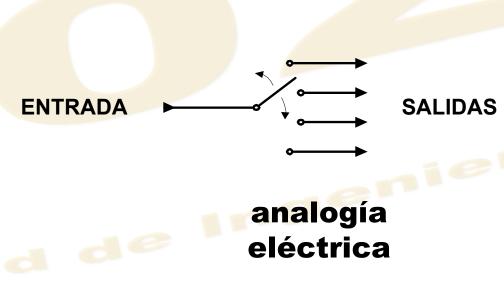

Es un circuito combinacional de una entrada y varias salidas, que puede "transferir" (reconstruir) la entrada a una de las salidas, mediante una codificación predefinida.

# 4 salidas/canales × 1 bit/canal

# n salidas/canales × 1 bit/canal

#### **Demultiplexores (DMPX)**

**Ejemplo:** Demultiplexor de 4x1 – Código binario natural

$Z_1 = S_1 . S_2 . E$

La síntesis directa es simple. Tantas AND como salidas. A cada AND ingresa la entrada E y las líneas de selección codificadas.

$Z_2 = \overline{S_1} \cdot S_1 \cdot E$

# CMP COMPARADORES

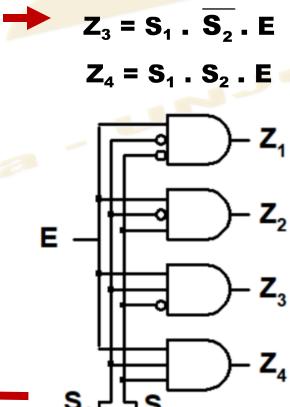

## **Comparadores (CPX)**

Floyd, pg. 344

Circuito combinacional de 2 x n entradas y una salida o más salidas, tal que produce resultado 1 en la o las salidas cuando las condiciones de comparación en las dos palabras binarias de n bits son verdaderas.

**Bloques genéricos**

La estructura se puede ampliar para comparar más de dos palabras. La comparación puede ser a igualdad, a mayor o a menor.

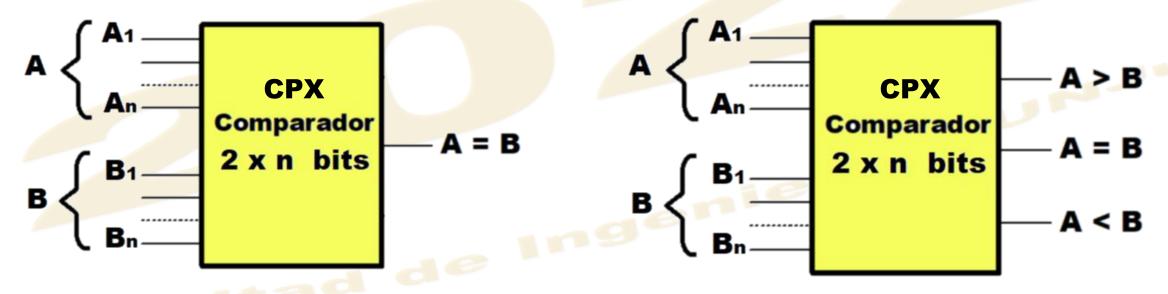

### **Comparadores (CPX)**

# Ejemplo: Diseño de un comparador de 4 bits a igualdad.

| Dec                     | <b>A1</b> | <b>A2</b> | А3 | <b>A4</b> | В1 | B2 | В3 | В4 | <b>Z1</b> |

|-------------------------|-----------|-----------|----|-----------|----|----|----|----|-----------|

| 010                     | 0         | 0         | 0  | 0         | 0  | 0  | 0  | 0  | 1         |

| 110                     | 0         | 0         | 0  | 1         | 0  | 0  | 0  | 1  | 1         |

| 210                     | 0         | 0         | 1  | 0         | 0  | 0  | 1  | 0  | 1         |

| 310                     | 0         | 0         | 1  | 1         | 0  | 0  | 1  | 1  | 1         |

| 410                     | 0         | 1         | 0  | 0         | 0  | 1  | 0  | 0  | 1         |

| <b>5</b> <sub>10</sub>  | 0         | 1         | 0  | 1         | 0  | 1  | 0  | 1  | 1         |

| 610                     | 0         | 1         | 1  | 0         | 0  | 1  | 1  | 0  | 1         |

| <b>7</b> <sub>10</sub>  | 0         | 1         | 1  | 1         | 0  | 1  | 1  | 1  | 1         |

| 810                     | 1         | 0         | 0  | 0         | 1  | 0  | 0  | 0  | 1         |

| 910                     | 1         | 0         | 0  | 1         | 1  | 0  | 0  | 1  | 1         |

| 1010                    | 1         | 0         | 1  | 0         | 1  | 0  | 1  | 0  | 1         |

| 1110                    | 1         | 0         | 1  | 1         | 1  | 0  | 1  | 1  | 1         |

| 1210                    | 1         | 1         | 0  | 0         | 1  | 1  | 0  | 0  | 1         |

| 1310                    | 1         | 1         | 0  | 1         | 1  | 1  | 0  | 1  | 1         |

| 1410                    | 1         | 1         | 1  | 0         | 1  | 1  | 1  | 0  | 1         |

| <b>15</b> <sub>10</sub> | 1         | 1         | 1  | 1         | 1  | 1  | 1  | 1  | 1         |

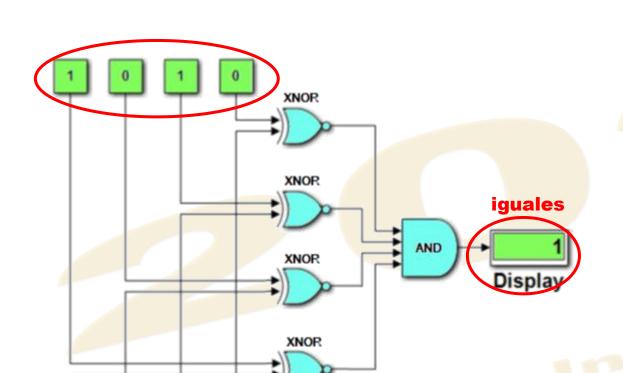

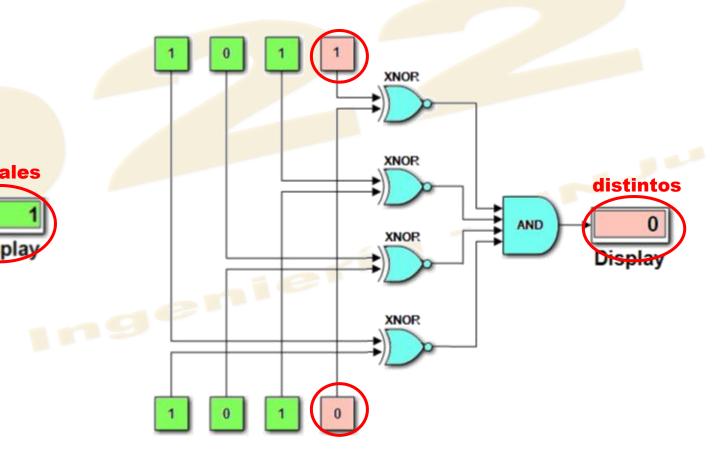

#### **Comparadores (CPX)**

Ejemplo: Diseño de un comparador de 4 bits a igualdad.

Simulación sobre Simulink de Matlab

# CDX CODIFICADORES

#### **Codificadores (CDX)**

Floyd, pg. 359 - Mano, pg. 139 - Dormido, pg. 441

Son circuitos combinacionales de m entradas y n salidas, que al recibir por las entradas una palabra binaria no codificado (ej. código posicional), produce a la salida la palabra equivalente codificada.

#### **Bloque genérico**

El proceso de diseño

consiste básicamente en

diseñar un circuito

combinacional que

asocie cada palabra

de entrada con la

correspondiente palabra

de salida codificada

Codificadores Sin prioridad a mayor

Con prioridad a menor

#### Código posicional decimal (1 de 10)

| <b>E</b> 9 | E8 | <b>E7</b> | <b>E</b> 6 | <b>E</b> 5 | <b>E4</b> | <b>E</b> 3 | E2 | E1 | E0 | Dec                    |

|------------|----|-----------|------------|------------|-----------|------------|----|----|----|------------------------|

| 0          | 0  | 0         | 0          | 0          | 0         | 0          | 0  | 0  | 1  | 010                    |

| 0          | 0  | 0         | 0          | 0          | 0         | 0          | 0  | 1  | 0  | 1 <sub>10</sub>        |

| 0          | 0  | 0         | 0          | 0          | 0         | 0          | 1  | 0  | 0  | <b>2</b> <sub>10</sub> |

| 0          | 0  | 0         | 0          | 0          | 0         | 1          | 0  | 0  | 0  | 3 <sub>10</sub>        |

|            |    |           |            |            |           |            |    |    |    |                        |

| 0          | 0  | 1         | 0          | 0          | 0         | 0          | 0  | 0  | 0  | <b>7</b> <sub>10</sub> |

| 0          | 1  | 0         | 0          | 0          | 0         | 0          | 0  | 0  | 0  | 8 <sub>10</sub>        |

| 1          | 0  | 0         | 0          | 0          | 0         | 0          | 0  | 0  | 0  | 9 <sub>10</sub>        |

#### Código posicional octal (1 de 8)

| <b>E7</b> | <b>E</b> 6 | <b>E</b> 5 | <b>E4</b> | <b>E3</b> | <b>E2</b> | E1 | E0 | Oct                   |

|-----------|------------|------------|-----------|-----------|-----------|----|----|-----------------------|

| 0         | 0          | 0          | 0         | 0         | 0         | 0  | 1  | 08                    |

| 0         | 0          | 0          | 0         | 0         | 0         | 1  | 0  | <b>1</b> <sub>8</sub> |

| 0         | 0          | 0          | 0         | 0         | 1         | 0  | 0  | <b>2</b> <sub>8</sub> |

| 0         | 0          | 0          | 0         | 1         | 0         | 0  | 0  | <b>3</b> <sub>8</sub> |

| 0         | 0          | 0          | 1         | 0         | 0         | 0  | 0  | <b>4</b> <sub>8</sub> |

| 0         | 0          | 1          | 0         | 0         | 0         | 0  | 0  | <b>5</b> <sub>8</sub> |

| 0         | 1          | 0          | 0         | 0         | 0         | 0  | 0  | <b>6</b> <sub>8</sub> |

| 1         | 0          | 0          | 0         | 0         | 0         | 0  | 0  | <b>7</b> 8            |

#### **Codificadores (CDX)**

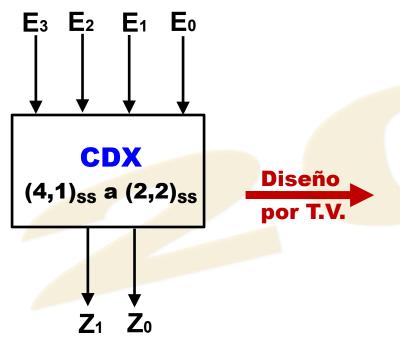

**Ejemplo:** Codificador sin prioridad de cuaternario (4,1)<sub>ss</sub> a binario natural (2,2)<sub>ss</sub>

| P              | osic           | al             | Binario |                |                |  |  |

|----------------|----------------|----------------|---------|----------------|----------------|--|--|

| E <sub>3</sub> | E <sub>2</sub> | E <sub>1</sub> | Eo      | Z <sub>1</sub> | Z <sub>0</sub> |  |  |

| 0              | 0              | 0              | 1       | 0              | 0              |  |  |

| 0              | 0              | 1              | 0       | 0              | 1              |  |  |

| 0              | 1              | 0              | 0       | 1              | 0              |  |  |

| 1              | 0              | 0              | 0       | 1              | 1              |  |  |

|                | Resta<br>nbin  | X              | X       |                |                |  |  |

Diagrama de bloque

Tabla de verdad reducida SIN PRIORIDAD

Circuito lógico

Nótese que en este caso que la implementación de variables, como la asignación de estados en las entradas, está implícita.

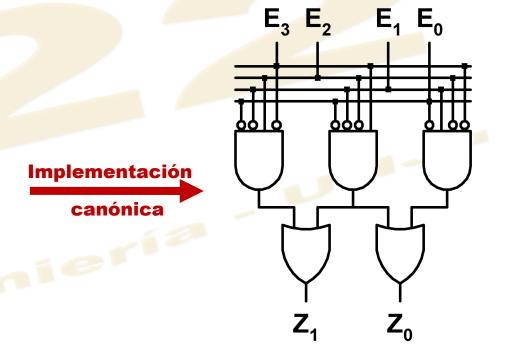

#### **Codificadores (CDX)**

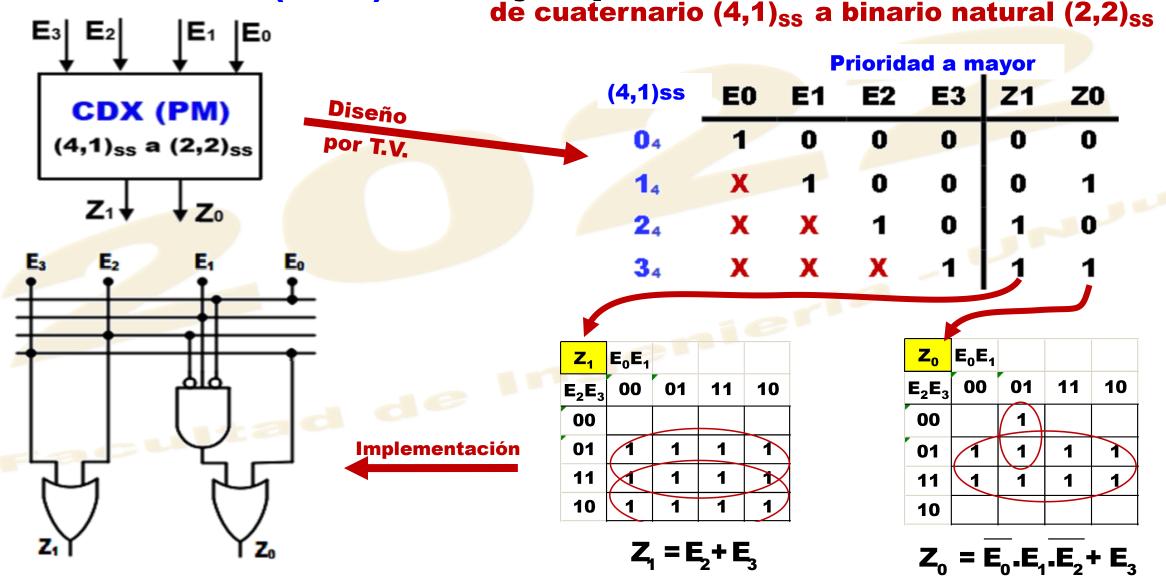

**Ejemplo:** Codificadores con prioridad de cuaternario (4,1)<sub>ss</sub> a binario natural (2,2)<sub>ss</sub>

Diagrama de bloque

Tablas de verdad reducidas

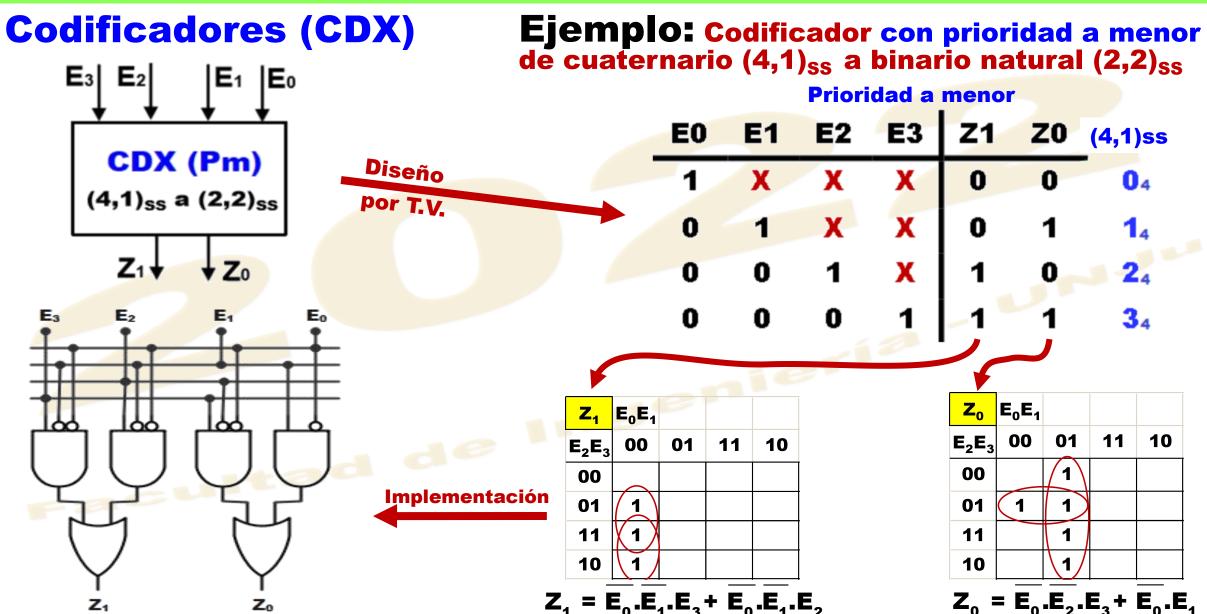

#### **Codificadores (CDX)**

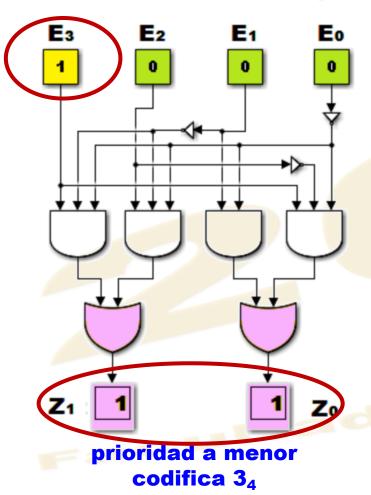

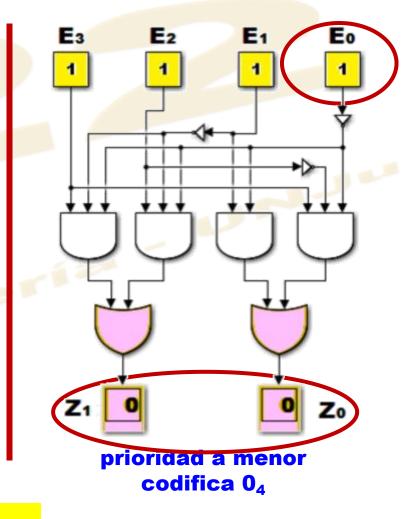

**Ejemplo:** Codificador con prioridad a menor de cuaternario  $(4,1)_{ss}$  a binario natural  $(2,2)_{ss}$

Simulación en Matlab

## **Codificadores (CDX)**

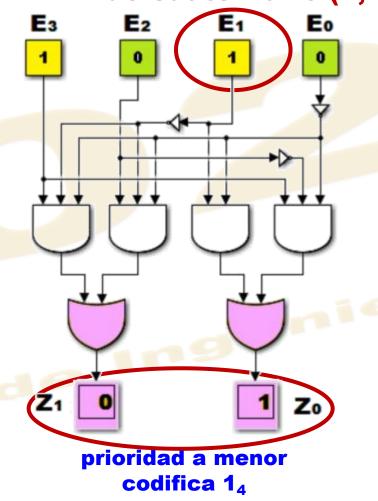

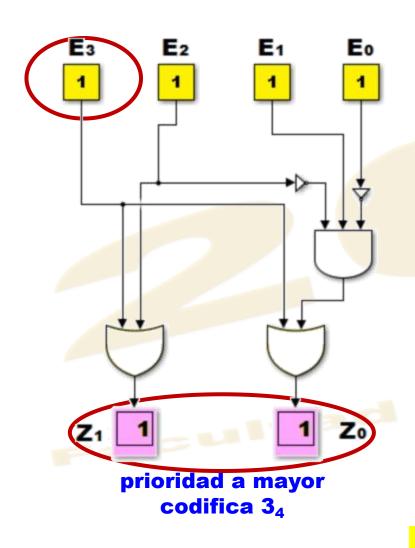

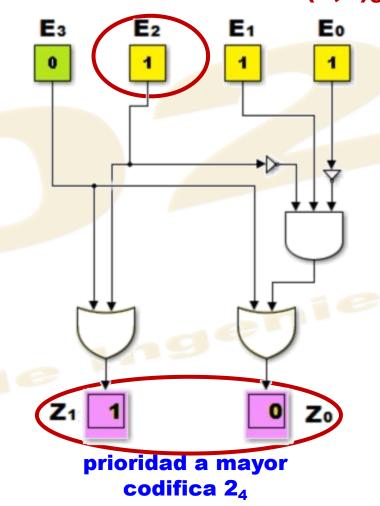

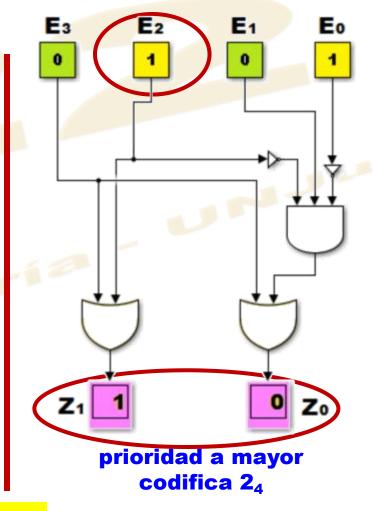

**Ejemplo:** Codificador con prioridad a mayor de cuaternario  $(4,1)_{ss}$  a binario natural  $(2,2)_{ss}$

#### **Codificadores (CDX)**

**Ejemplo:** Codificador con prioridad a mayor de cuaternario  $(4,1)_{ss}$  a binario natural  $(2,2)_{ss}$

Simulación en Matlab

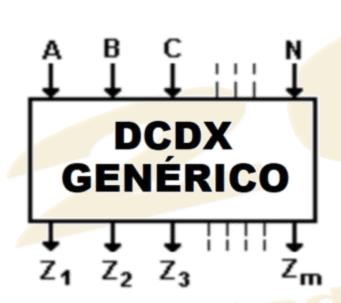

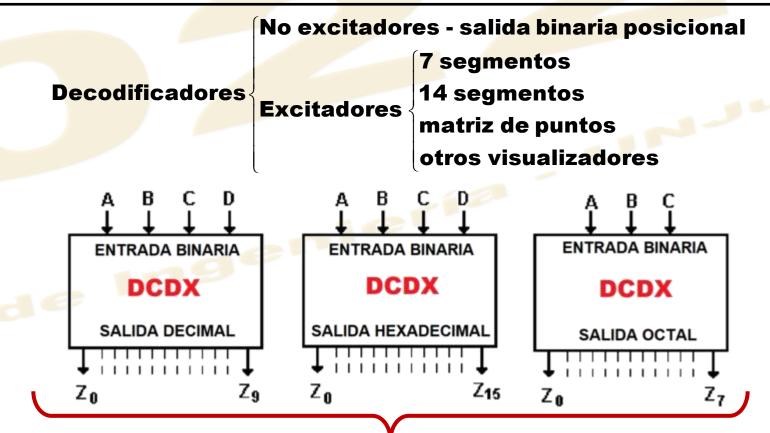

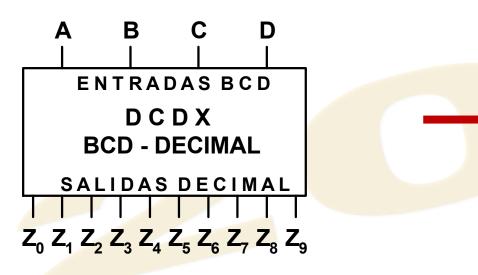

# DCDX DECODIFICADORES

#### **Decodificadores (DCDX)**

Mano, pg. 134 - Dormido, pg. 446

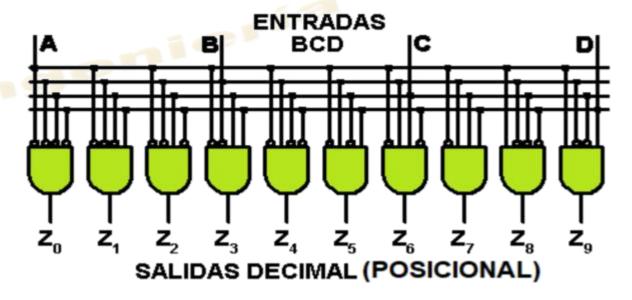

Son circuitos combinacionales de N líneas de entradas y m líneas de salida, que al recibir una secuencia binaria en un código preestablecido, produce a la salida un valor equivalente sin codificar (código posicional).

No excitadores - código posicional

#### **Decodificadores (DCDX)**

Ejemplo: Decodificador BCD natural a decimal no excitador.

| # | ABCD | Z <sub>0</sub> | Z <sub>1</sub> | Z <sub>2</sub> | <b>Z</b> <sub>3</sub> | Z <sub>4</sub> | Z <sub>5</sub> | Z <sub>6</sub> | <b>Z</b> <sub>7</sub> | Z <sub>8</sub> | Z <sub>9</sub> |

|---|------|----------------|----------------|----------------|-----------------------|----------------|----------------|----------------|-----------------------|----------------|----------------|

| 0 | 0000 | 1              | 0              | 0              | 0                     | 0              | 0              | 0              | 0                     | 0              | 0              |

| 1 | 0001 | 0              | 1              | 0              | 0                     | 0              | 0              | 0              | 0                     | 0              | 0              |

| 2 | 0010 | 0              | 0              | 1              | 0                     | 0              | 0              | 0              | 0                     | 0              | 0              |

| 3 | 0011 | 0              | 0              | 0              | 1                     | 0              | 0              | 0              | 0                     | 0              | 0              |

| 4 | 0100 | 0              | 0              | 0              | 0                     | 1              | 0              | 0              | 0                     | 0              | 0              |

| 5 | 0101 | 0              | 0              | 0              | 0                     | 0              | 1              | 0              | 0                     | 0              | 0              |

| 6 | 0110 | 0              | 0              | 0              | 0                     | 0              | 0              | 1              | 0                     | 0              | 0              |

| 7 | 0111 | 0              | 0              | 0              | 0                     | 0              | 0              | 0              | 1                     | 0              | 0              |

| 8 | 1000 | 0              | 0              | 0              | 0                     | 0              | 0              | 0              | 0                     | 1              | 0              |

| 9 | 1001 | 0              | 0              | 0              | 0                     | 0              | 0              | 0              | 0                     | 0              | 1              |

|   | Co   | mbin           | acior          | nes re         | estan                 | tes n          | o utili.       | zada           | S                     |                |                |

#### **Decodificadores (DCDX) excitadores**

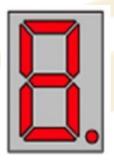

Los decodificadores identificados como excitadores, en vez de dar salida en un código posicional, se diseñan para generar un código especial que sea capaz de activar algún dispositivo visualizador, interpretable por un usuario.

Los dispositivos visualizadores (displays) más comunes se muestran abajo, siendo el de 7 segmentos el más usual.

7 segmentos

14 segmentos

tubo nixie

16 segmentos alfanumérico

matriz de puntos alfanumérico

Dígito 7 segmentos: Son segmentos independientes de diodos led, que se disponen como en la figura. Cada segmento/diodo, al recibir un '1' lógico se enciende.

#### **Decodificadores (DCDX)**

Floyd, pg. 356

#### Ejemplo: Decodificador excitador de BCD a 7 segmentos

Cada segmento del display se identifica con una letra (de a hasta g). La estrategia para construir la TV es marcar con '1' aquellos segmentos que deban formar el dígito.

|     | Ent | rad | la E | BCD | Sa | alid | a 7 | se | gme | ente | os |   |

|-----|-----|-----|------|-----|----|------|-----|----|-----|------|----|---|

| dec | A   | В   | C    | D   | а  | b    | С   | d  | е   | f    | g  |   |

| 0   |     |     | 0    | 0   | 1  | 1    | 1   | 1  | 1   | 1    | 0  |   |

| 1   |     | 0   | 0    | 1   | 0  | 1    | 1   | 0  | 0   | 0    | 0  |   |

| 2   | U   | U   | 1    | 0   | 1  | 1    | 0   | 1  | 1   | 0    | 1  |   |

| 3   |     |     | 1    | 1   | 1  | 1    | 1   | 1  | 0   | 0    | 1  |   |

| 4   |     |     | 0    | 0   | 0  | 1    | 1   | 0  | 0   | 1    | 1  |   |

| 5   | 0   | 4   | 0    | 1   | 1  | 0    | 1   | 1  | 0   | 1    | 1  |   |

| 6   | 0   | •   | 1    | 0   | 1  | 0    | 1   | 1  | 1   | 1    | 1  |   |

| 7   |     |     |      | 1   | 1  | 1    | 1   | 1  | 0   | 0    | 0  | 0 |

| 8   | 4   | 0   | 0    | 0   | 1  | 1    | 1   | 1  | 1   | 1    | 1  |   |

| 9   | Sh  |     | 0    | 1   | 1  | 1    | 1   | 1  | 0   | 1    | 1  |   |

| 1 | 2 | т | Ŧ | 5 | 5 | ۲- | 8 | 9 |   |

|---|---|---|---|---|---|----|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7  | 8 | 9 | 0 |

Un procedimiento similar se puede seguir para configurar el código de salida en los otros displays, sólo tener en cuenta la cantidad de segmentos y el diseño de los caracteres.

#### **Decodificadores (DCDX)**

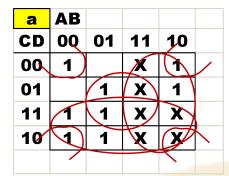

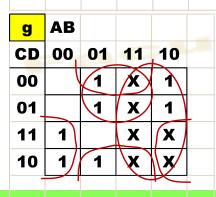

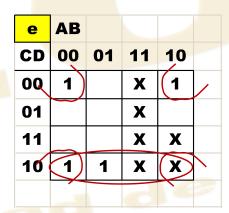

#### Ejemplo: Decodificador excitador de BCD a 7 segmentos (continuación)

| d  | AB |    |    |               |  |

|----|----|----|----|---------------|--|

| CD | 00 | 01 | 11 | 10            |  |

| 00 | 1  | 1  | X  | $\rightarrow$ |  |

| 01 |    |    | X  | 1             |  |

| 11 | 1  |    | X  | X             |  |

| 10 | 1  | 1  | X  | X             |  |

|    |    |    |    |               |  |

| b  | AB                                 |    |    |    |

|----|------------------------------------|----|----|----|

| CD | 00                                 | 01 | 11 | 10 |

| 00 | $\left\langle \cdot \right\rangle$ | 1  | X  |    |

| 01 | <b>/</b> _                         |    | X  | 1  |

| 11 | (+)                                | 1  | X  | X  |

| 10 | 1                                  |    | X  | W  |

| С   | AB                     |    |    |              |           |

|-----|------------------------|----|----|--------------|-----------|

| CD  | 00                     | 01 | 11 | 10           |           |

| 00/ | 1                      | 1  | X  | 1            |           |

| 01  | 1                      | 1  | X  | <del>(</del> | $\langle$ |

| 11  | <b>/</b> <del>-/</del> | 1  | X  | X            |           |

| 10  |                        | 1  | X  | X            |           |

|     |                        |    |    |              |           |

| f  | AB |    |    |              |

|----|----|----|----|--------------|

| CD | 00 | 01 | 11 | 10           |

| 00 | 1  | (1 | X  |              |

| 01 |    | 1  | X  | 1            |

| 11 |    |    | X  | X            |

| 10 |    | 1  | X  | \ <b>y</b> / |

|    |    |    |    | 7            |

En este caso, se han utilizado las combinaciones mayores a 9<sub>10</sub>, como salidas indefinidas, aprovechables por Karnaugh.

$$a = A + C + B.D + \overline{B}.\overline{D}$$

$$b = A + \overline{B} + \overline{C}.\overline{D} + C.D$$

$$c = B + \overline{C} + D_{\bullet}$$

$$d = A + \overline{D} + \overline{A}.B.C$$

$$e = \overline{B}.\overline{D} + C.\overline{D}$$

$$f = A + B.\overline{C} + B.\overline{D} + \overline{C}.\overline{D}$$

$$g = A + B.\overline{C} + B.\overline{D} + \overline{B}.C$$

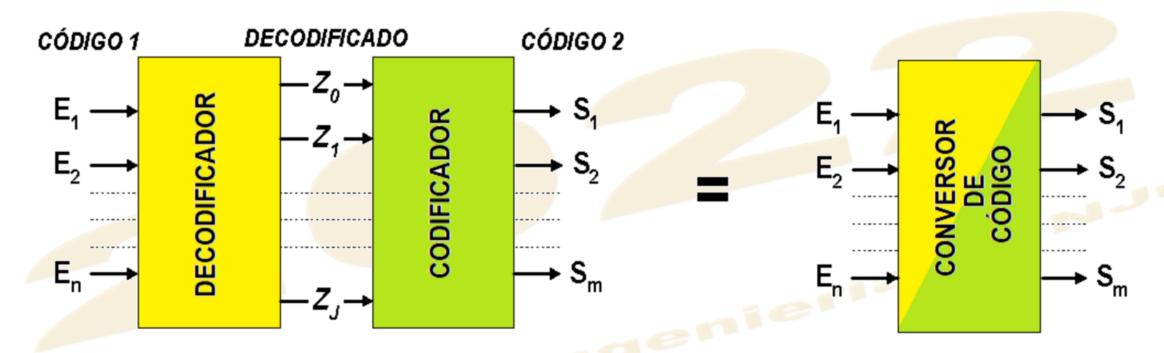

# CCDX CONVERSORES DE CÓDIGO

#### Conversores de código

Floyd, pg. 364

El conversor de código puede verse como la asociación de un decodificador y un codificador.

El diseño se realiza directamente desde el código 1 (como entrada) al código 2 (como salida).

Eventualmente se pueden diseñar por separado y acoplar.

#### Conversor de código

Ejemplo: Conversor de código

de BCD 2 de 5 a BCD 2 de 7.

| D  | Α | В    | С       | D     | Е | Т | U | V    | W       | X     | Y | Z |

|----|---|------|---------|-------|---|---|---|------|---------|-------|---|---|

| E  |   | Pesc | os (2 d | de 5) |   |   |   | Pesa | os (2 i | de 7) |   |   |

| C. | 0 | 1    | 2       | 3     | 6 | 5 | 0 | 4    | 3       | 2     | 1 | 0 |

| 0  | 0 | 1    | 1       | 0     | 0 | 0 | 1 | 0    | 0       | 0     | 0 | 1 |

| 1  | 1 | 1    | 0       | 0     | 0 | 0 | 1 | 0    | 0       | 0     | 1 | 0 |

| 2  | 1 | 0    | 1       | 0     | 0 | 0 | 1 | 0    | 0       | 1     | 0 | 0 |

| 3  | 1 | 0    | 0       | 1     | 0 | 0 | 1 | 0    | 1       | 0     | 0 | 0 |

| 4  | 0 | 1    | 0       | 1     | 0 | 0 | 1 | 1    | 0       | 0     | 0 | 0 |

| 5  | 0 | 0    | 1       | 1     | 0 | 1 | 0 | 0    | 0       | 0     | 0 | 1 |

| 6  | 1 | 0    | 0       | 0     | 1 | 1 | 0 | 0    | 0       | 0     | 1 | 0 |

| 7  | 0 | 1    | 0       | 0     | 1 | 1 | 0 | 0    | 0       | 1     | 0 | 0 |

| 8  | 0 | 0    | 1       | 0     | 1 | 1 | 0 | 0    | 1       | 0     | 0 | 0 |

| 9  | 0 | 0    | 0       | 1     | 1 | 1 | 0 | 1    | 0       | 0     | 0 | 0 |

$T = \overline{A} \overline{B}.C.D.\overline{E} + A \overline{B}.\overline{C}.\overline{D}.E + \overline{A}B.\overline{C}.\overline{D}.E + \overline{A}\overline{B}.C.\overline{D}.E + \overline{A}\overline{B}.\overline{C}.D.E$  $U = \overline{A}B.C.\overline{D}.\overline{E} + AB.\overline{C}.\overline{D}.\overline{E} + AB.\overline{C}.\overline{D}.\overline{E} + \overline{A}B.\overline{C}.\overline{D}.\overline{E} + \overline{A}B.\overline{C}.\overline{D}.\overline{E}$  $V = \overline{A}B.\overline{C}.D.\overline{E} + \overline{A}B.\overline{C}.D.\overline{E}$  $W = A \overline{B}. \overline{C}. D. \overline{E} + \overline{A} \overline{B}. C. \overline{D}. E$ X = AB.C.D.E + AB.C.D.E $Y = AB.\overline{C}.\overline{D}.\overline{E} + AB.\overline{C}.\overline{D}.\overline{E}$  $Z = \overline{AB.C.D.E} + \overline{AB.C.D.E}$

#### Conversor de código

Floyd, pg. 366

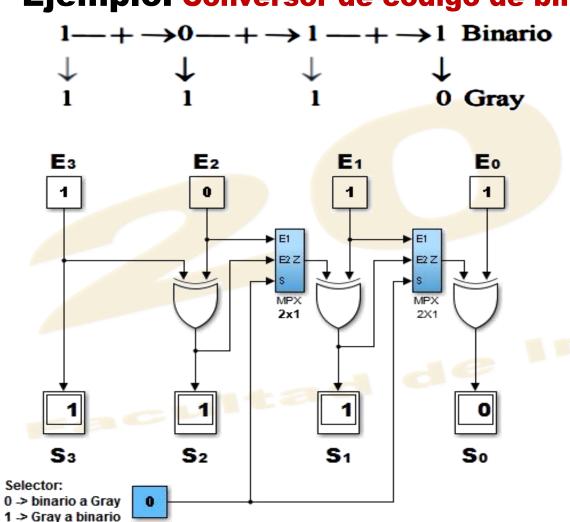

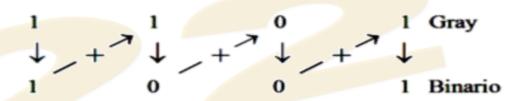

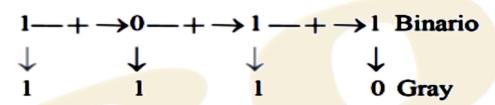

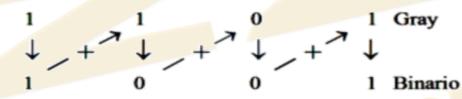

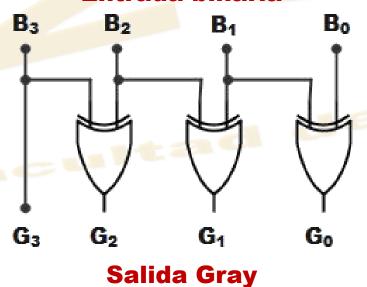

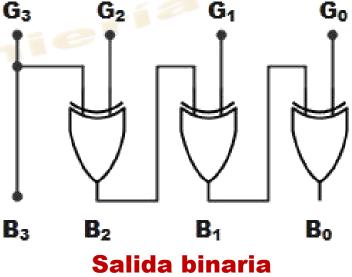

#### Ejemplo: Conversor de código de binario natural a Gray y viceversa.

Este modelo se puede realizar mediante el procedimiento estándar con la tabla de verdad. Aunque es más sencillo (y es equivalente) utilizar el algoritmo de conversión, como se muestra.

#### **Entrada binaria**

## Entrada Gray

#### Conversor de código

Floyd, pg. 366

Ejemplo: Conversor de código de binario natural a Gray y viceversa (continuación)

**Matlab**